Exploring Open Hardware: Hands-on with RISC-V Core

📅 4/22/2025 ⏳ 5 minutes read ✍️ Yusron Izza

🗂️ Category : Verilog, CPU

"In the age of open-source innovation, RISC-V stands out as a game-changer in processor design. In this article, I will share my experiences of prototyping processor using Verilog. Whether you're a student, hobbyist, or just curious about custom CPU development, I will talk about the practical steps, challenges, and insights I gained while exploring this powerful instruction set architecture."

In the rapidly evolving world of computing, RISC-V has emerged as a powerful and open alternative to traditional instruction set architectures. Unlike proprietary architectures such as x86 or ARM, RISC-V is open-source, allowing anyone to study, modify, and implement it freely. This openness has sparked interest among researchers, students, and companies looking to innovate without licensing restrictions. As an electrical engineering graduate with a deep curiosity in digital system design, I found RISC-V to be an ideal starting point to explore processor architecture from the ground up.

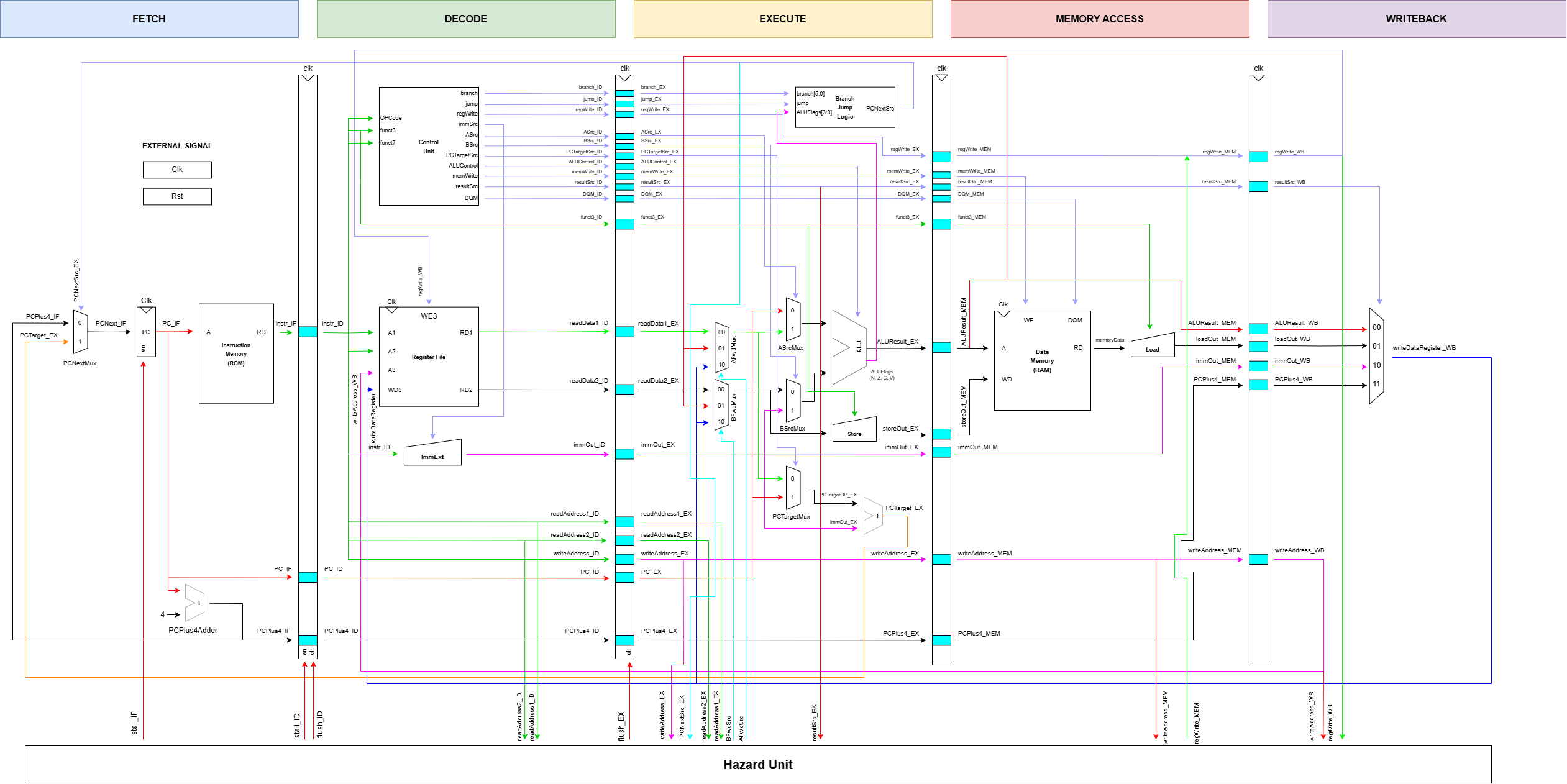

My journey into RISC-V began with learning the fundamentals of the instruction set, focusing on the RV32I base integer instruction set. To truly understand how a processor works, I decided to build my own RISC-V processor using Verilog. This project became a hands-on way for me to apply my theoretical knowledge in digital design and test it using simulation tools. Designing each module—from the instruction fetch and decode units to the ALU and register file—gave me valuable insight into how processors execute instructions step by step.

Image shows my own architecture diagram of RISC-V core processor with 5 stage of pipeline

One of the most exciting parts of the project was implementing pipelining, a technique that allows multiple instructions to be processed simultaneously, increasing overall performance. Debugging pipeline hazards, managing control flow, and optimizing instruction throughput were all challenging yet rewarding experiences. I also built a simple test bench to verify the functionality of my core, running a few RISC-V assembly programs to see it all in action. Watching my design execute instructions correctly was a huge milestone.

This project not only strengthened my understanding of digital design and computer architecture but also deepened my interest in embedded systems and hardware-software co-design. It taught me that working on low-level systems requires both precision and creativity. I’m now exploring how I can integrate my RISC-V core with peripherals or even boot a minimal operating system on it. My long-term goal is to contribute to the open-source RISC-V ecosystem and perhaps design a system-on-chip (SoC) for educational and open-source project.

I hope that sharing my experience encourages you to explore the world of RISC-V. Whether you're interested in processor design, hardware acceleration, or secure computing, RISC-V provides a flexible platform for experimentation and learning. This project is not perfect yet. The architecture currently can only run basic instructions, such as RISCV-32I (Base Integer). In the future, extensions like M and A will be added. (Do you know about M, A extension? I will talk about it later). I hope this design would be able to run OS like Linux. This journey is only the beginning, and I look forward to exploring what more I can build with open hardware. Visit my project HERE